SL1620用户指南

介绍

Astra Foundation系列评估套件 使 SL系列多模式嵌入式处理器能够轻松快速地进行原型设计。 模块化设计包含可更换的核心计算模块、通用I/O板和子卡,用于连接、调试和灵活的I/O选项。

Synaptics Astra SL系列是一个高度集成的人工智能原生Linux和Android SoC系列, 针对多模式消费者、企业和工业物联网工作负载进行了优化, 具有边缘推理、安全、图形、视觉和音频的硬件加速器。 SL1620专为需要强大处理、高级人工智能功能和3D图形的嵌入式应用程序而设计和优化。 该芯片配有Linux®操作系统、卓越的音频算法、各种外围设备、双显示器、用于连接和音频前端的配套Synaptics SoC。

范围

本用户指南介绍了 Astra系列 AI开发套件 SL1620核心模块、I/O卡和支持的子卡的硬件配置和功能细节, 以及评估套件的点亮顺序。

板卡组件定义

Astra系列 AI开发套件 : 由核心模块、I/O板和支持的子卡构成的组合系统。

核心模块 : 处理器子系统模块,包括SL1620、eMMC和LPDDR4x等关键组件。

I/O板 : 通用基板,包括各种标准硬件接口、按钮、接头和电源输入。

子卡 : 用于支持各种功能的附加板,如连接、调试和其他灵活的I/O选项。

Astra系列 AI开发套件概述

本节介绍 Astra系列 AI评估套件的系统功能、框图和俯视图。

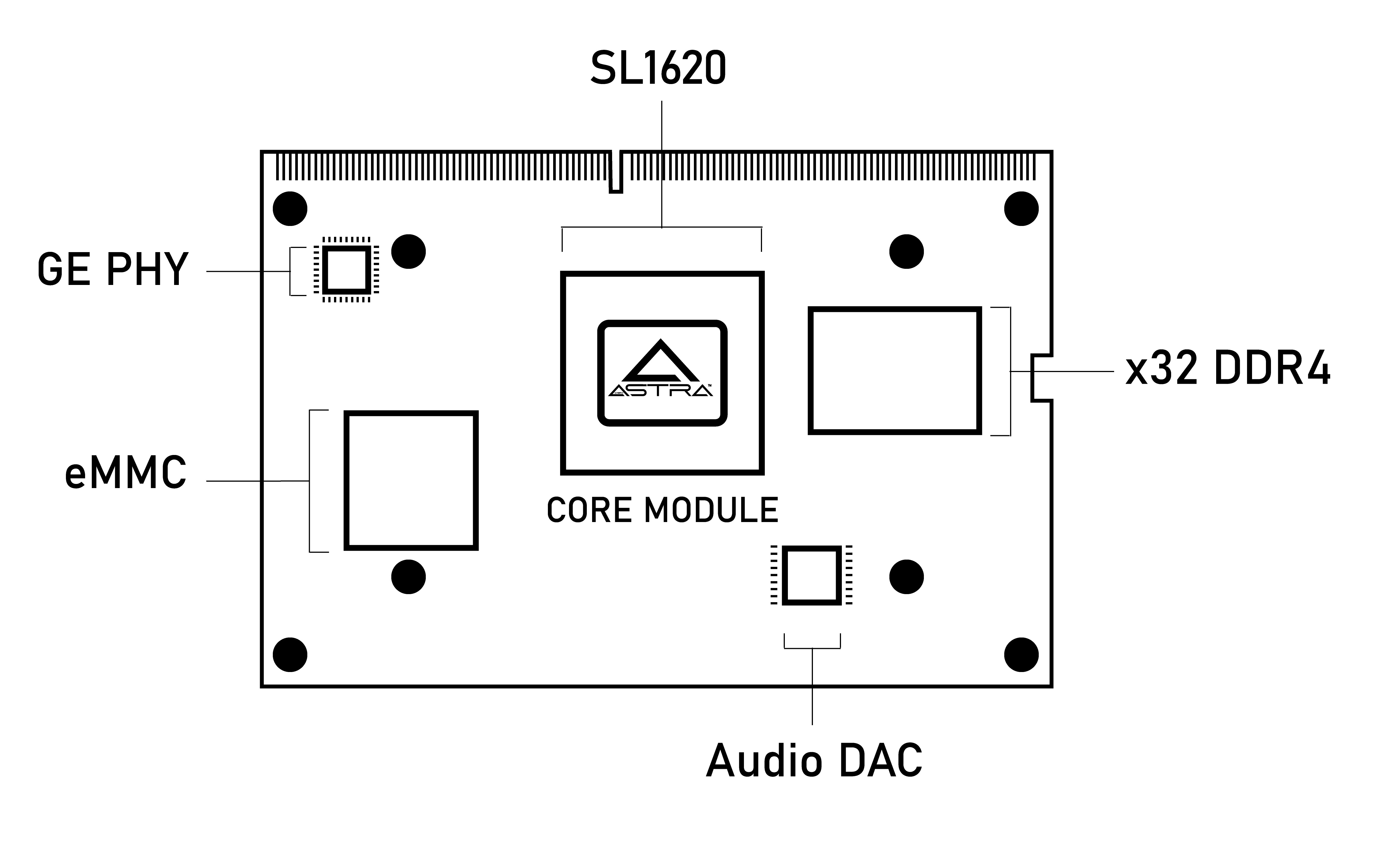

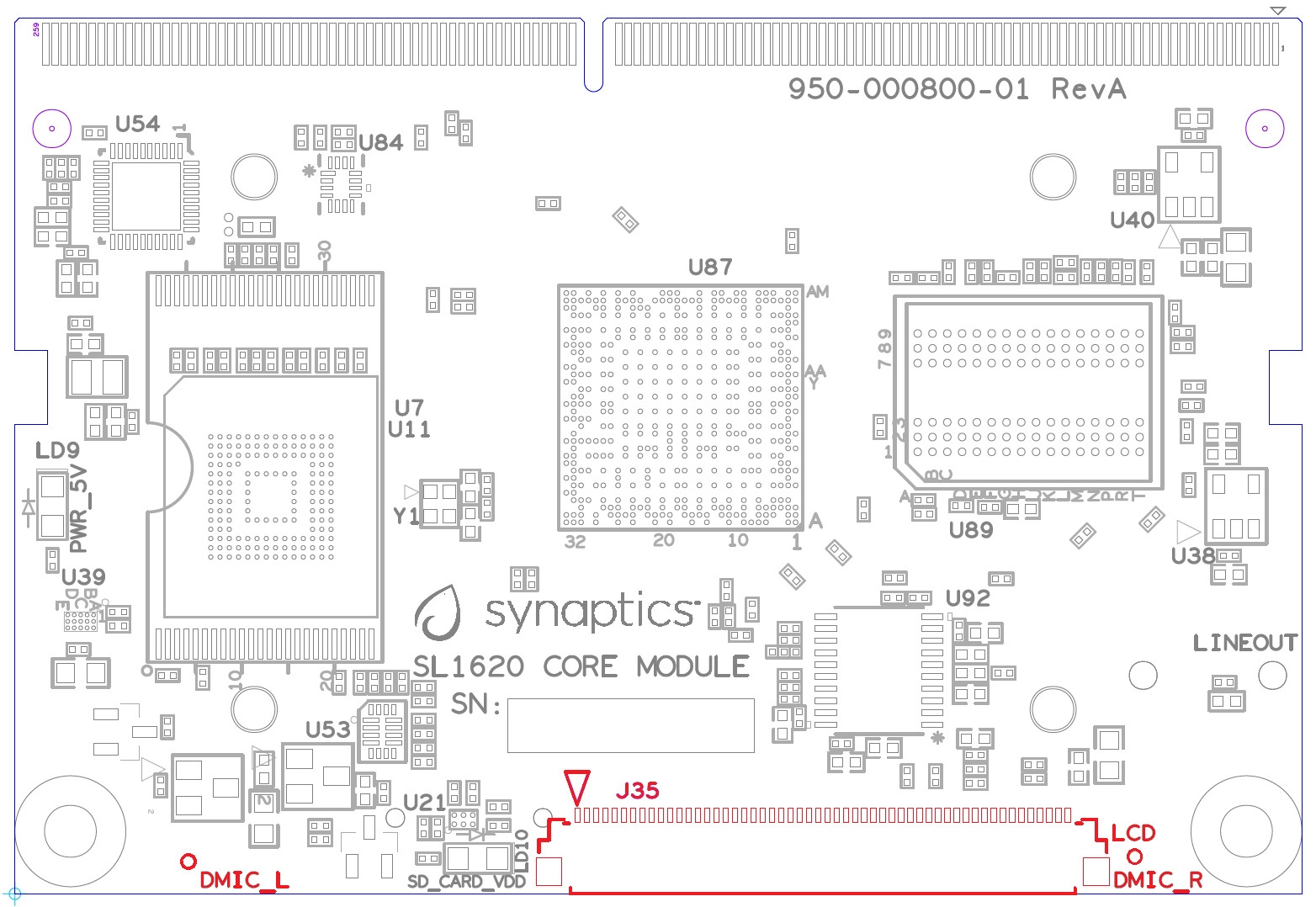

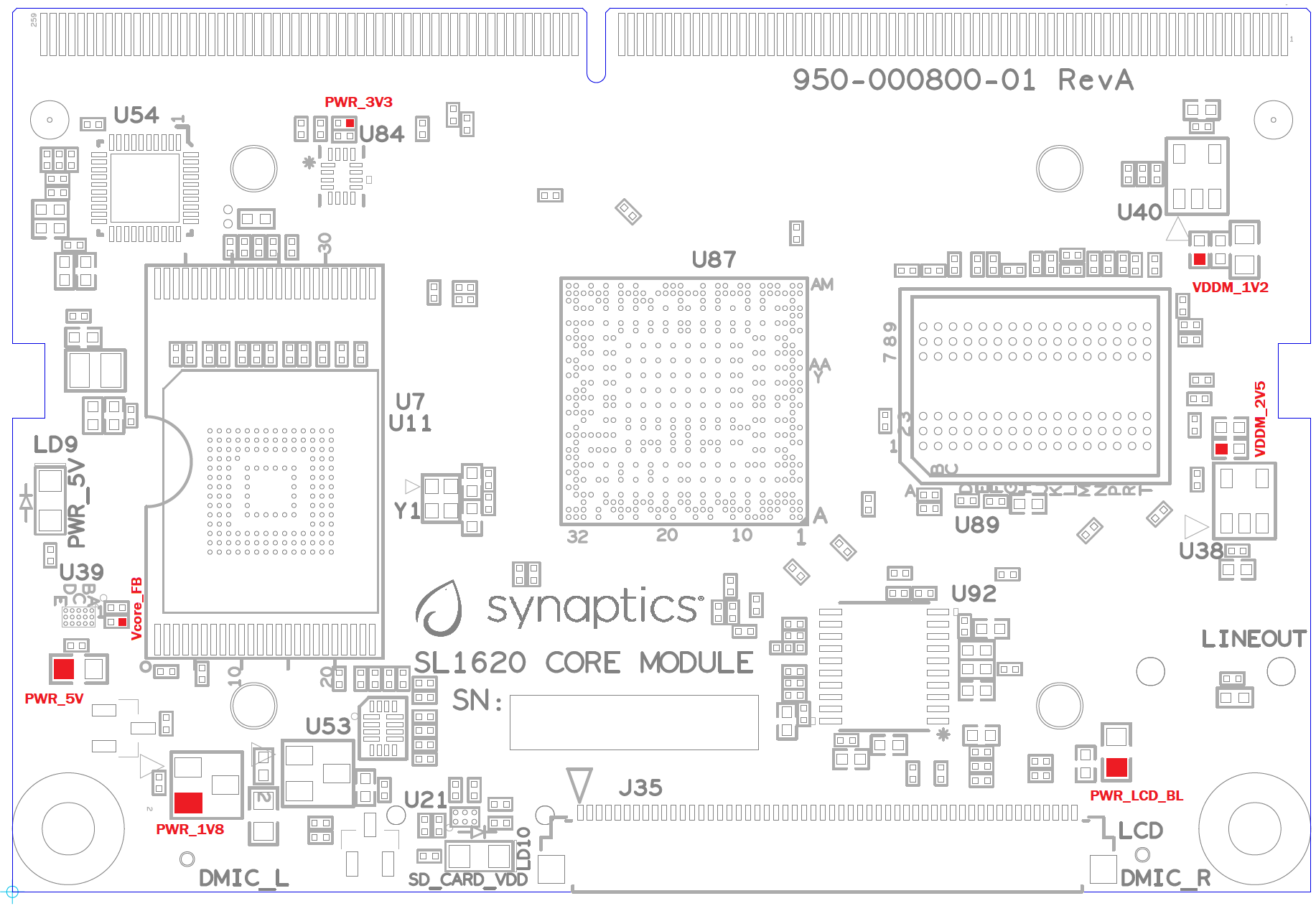

SL1620核心模块(尺寸:宽x高= 69.6 x 47.38mm)

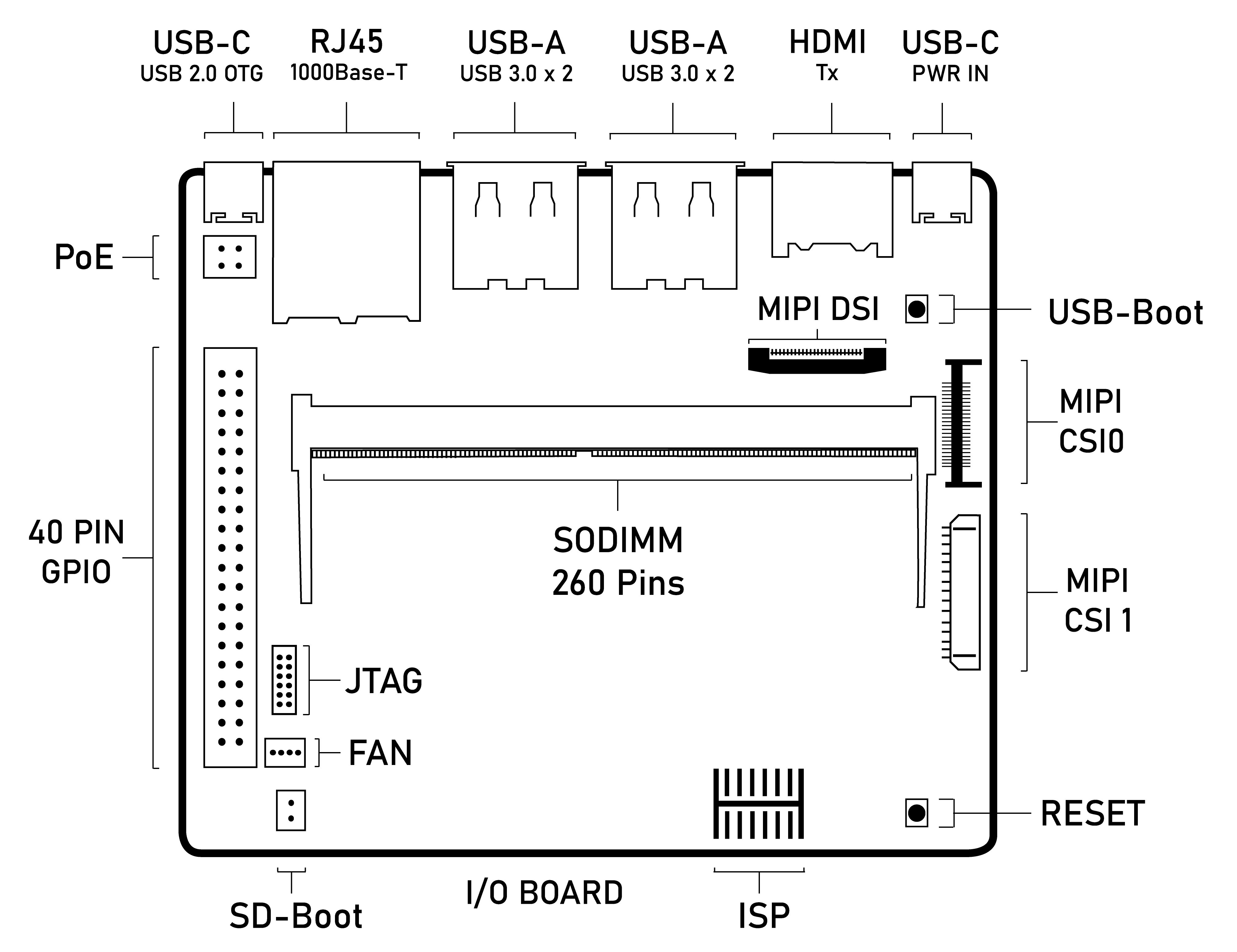

I/O板

特征

基于 SL1620 的评估系统包括以下组件:

核心模块上的主要组件:

Synaptics SL1620四核ARM Cortex-A55

嵌入式物联网处理器,高达1.9 GHz。

存储:eMMC5.1(16 GByte)。

DRAM:x32 2GB系统内存,使用2颗 x16 8-Gbit LPDDR4x。

PMIC:支持Vcore供电轨中的DVFS。

SD卡插座。

Line Out:直接Line Level 2.1-VRMS 立体声输出。

DMIC:两个数字麦克风 — 1个PDM立体声音频输入。

LCDC(RGB): 在54引脚FPC连接器上,支持RGB 16bpp、18bpp和24bpp输出格式;高达1080p30屏幕分辨率。

I/O板上的主要组件:

M.2 E-key 2230插座: 支持用于Wi—Fi/BT模块的SDIO、PCIe、UART。

USB 3.0 Type-A:4个端口,支持SuperSpeed主机模式。

USB 2.0 Type-C:支持高速OTG主机或外设模式。

按钮:用于USB-BOOT选择和系统重启。

2针接头:用于SD-BOOT选择。

外接子卡接口选项:

MIPI DSI 在22针FPC接口上, 支持4-lane DPHY加I2C和GPIO,用于最高1080p60的显示面板。

ISP 12针子卡, 支持核心模块上离线编程的SPI NOR闪存。

调试用的JTAG子卡。

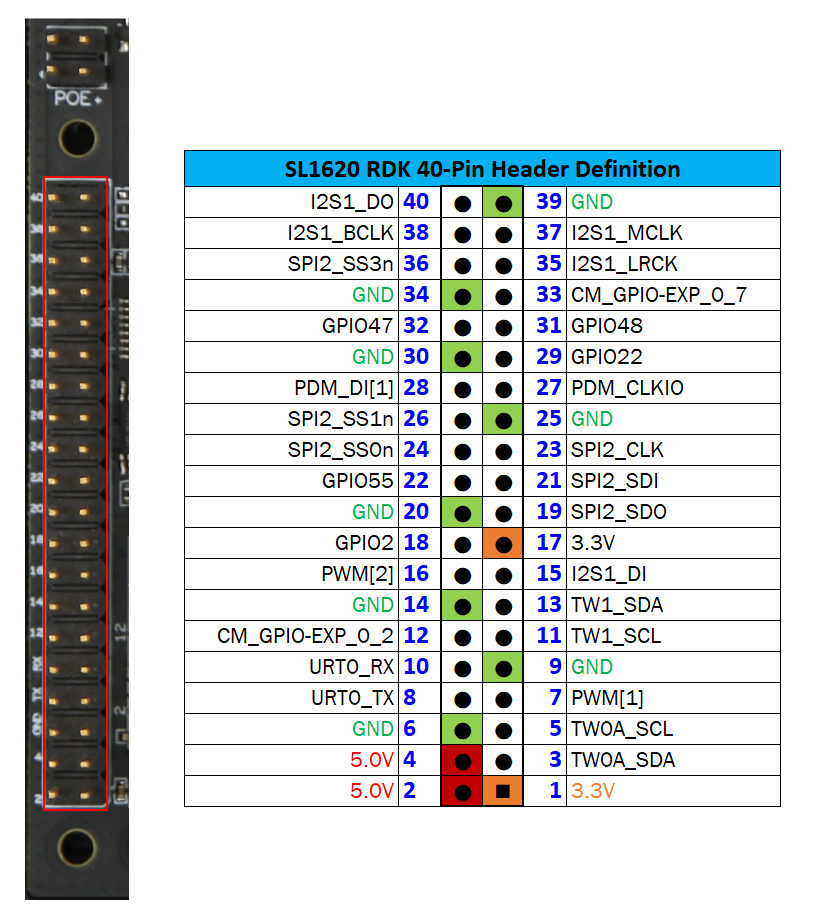

40-针接头用于附加功能。

4针 PoE+ 子卡, 支持 PoE+Type2(802.3at)电源设备的附加电压调节器模块。在40针接头到I/O板的5V引脚处,可用功率应为25.5W(4级)。

PWM有源风扇的4针接头。

Type—C电源,15V @ 1.8A。

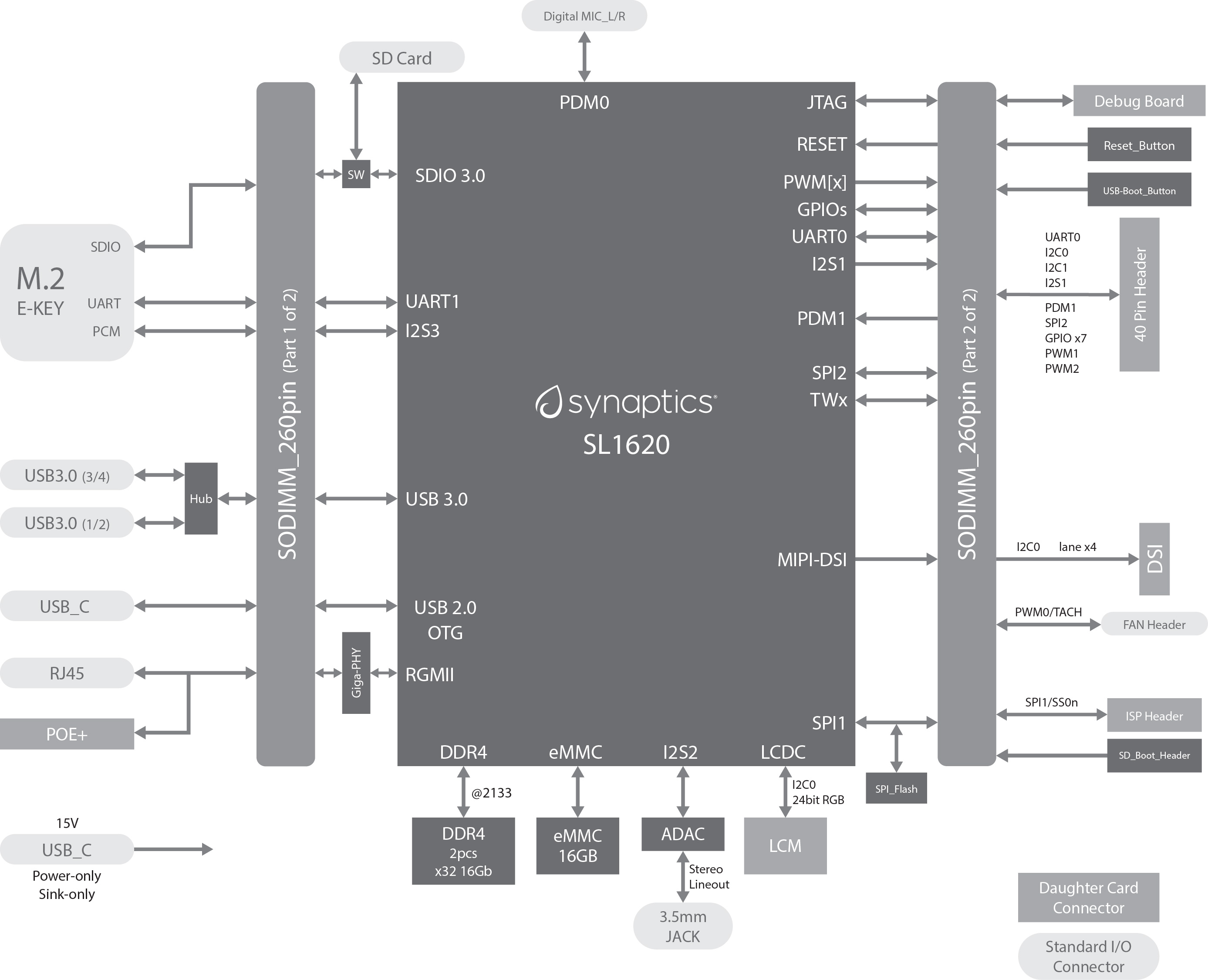

SL16200系统框图

SL1620系统框图

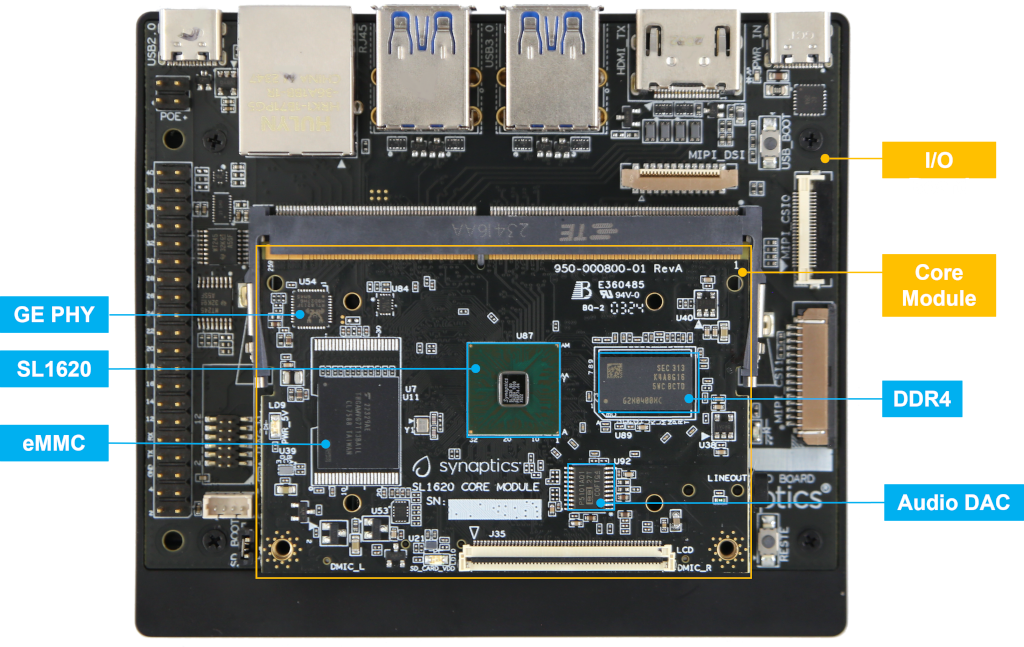

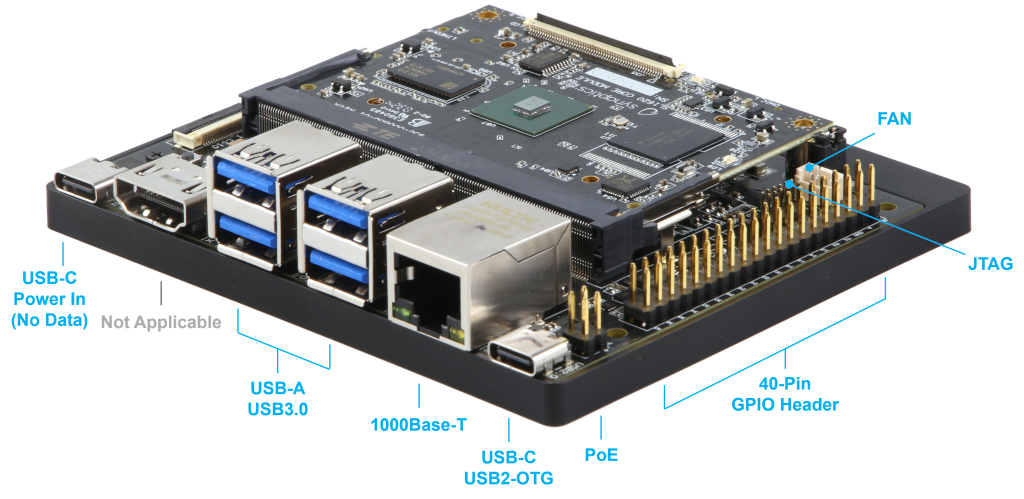

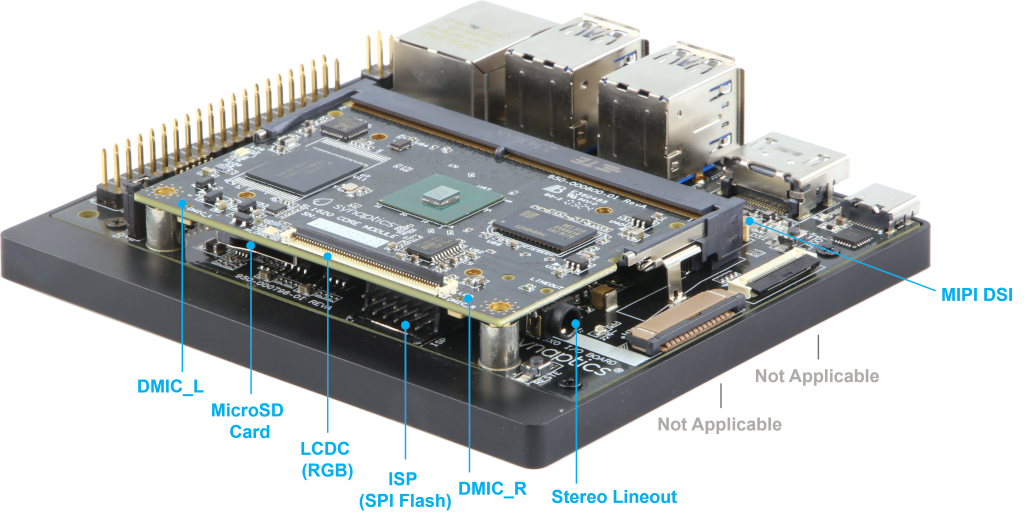

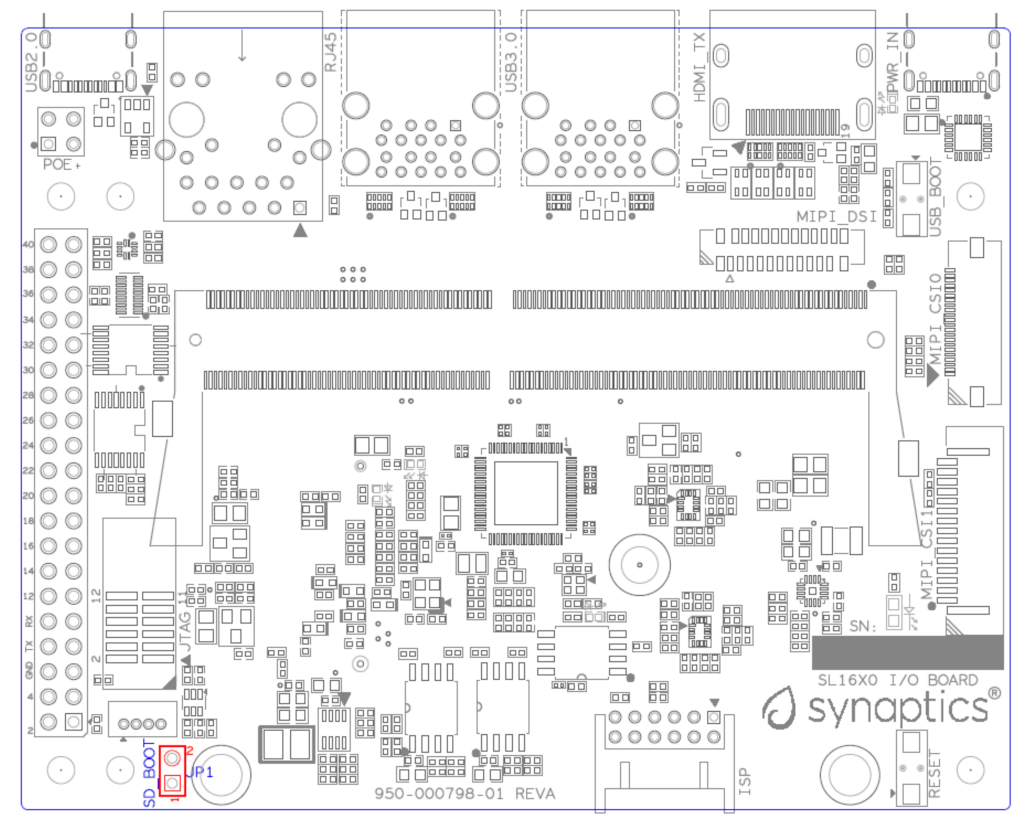

SL1620 Astra系列 AI评估系统的俯视图

SL1620评估系统俯视图

系统连接器

前视图

后视图

Astra系列板控制/状态&系统I/O

本节介绍启动、LED状态指示灯、按钮,连接器和pin-strap设置。

启动

Astra开发套件支持三种启动方式, 上电前用户可选一种。

eMMC启动 :默认启动方式。

SD启动 :通电前用2.54mm跳线帽短接SD_Boot接头,请参阅 I/O板上跳线的位置图 中的SD_Boot接头。 确保烧好固件的SD卡已插入核心模块上的SD插槽中,请参阅 核心模块背面的连接器位置 。

USB启动 :将USB—C usb2.0端口连接到主机PC,然后按照第2.4节中的步骤操作。

LED指示灯

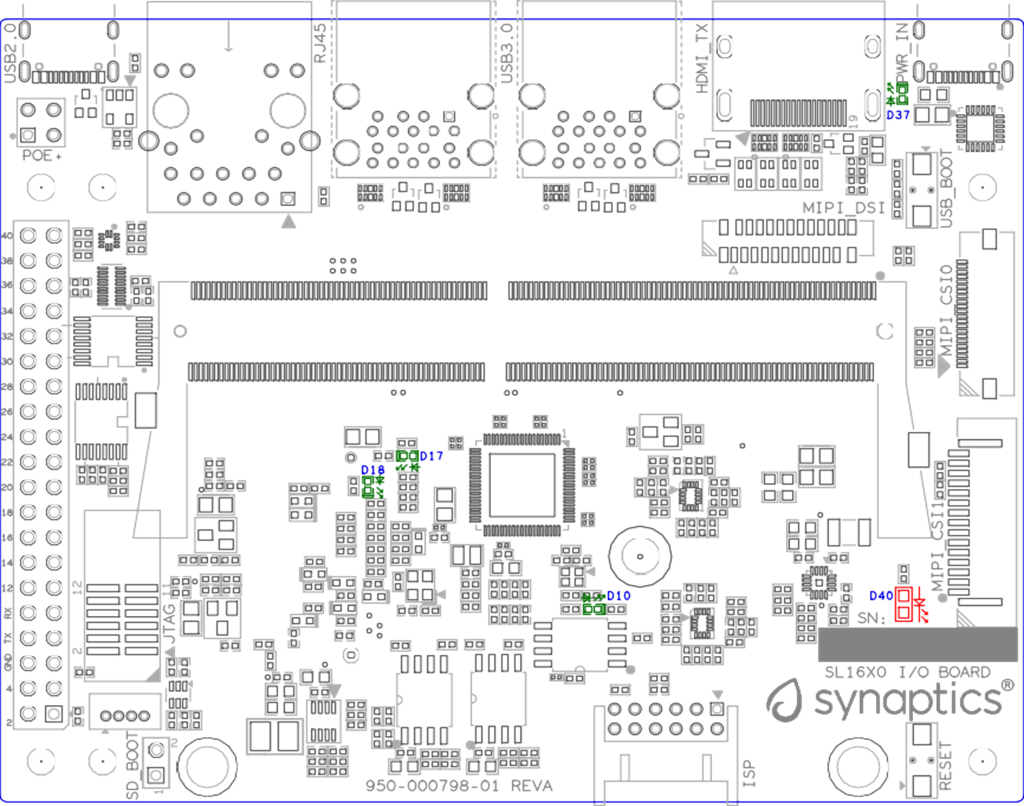

LED指示灯的位置

I/O板上的LED位置图 显示I/O板上的LED位置。

I/O板上的LED位置图

LED定义

LED |

颜色 |

LED功能 |

|---|---|---|

D10 |

绿色 |

LED指示灯用于标识USB3.0 Hub当前工作在正常模式下还是挂起模式下。 |

D17 |

绿色 |

LED指示灯1用于标识M.2设备的通用用途。 |

D18 |

绿色 |

LED指示灯2用于标识M.2设备的通用用途。 |

D37 |

绿色 |

LED指示灯用于标识USB-C PD电源的状态。 |

D40 |

红色 |

LED指示灯用于标识待机状态。 |

SoC PinStrap和启动设置

Pad名称 |

Strap名称 |

|

|

|

|---|---|---|---|---|

TEST_EN |

TEST_EN |

— |

— |

SM TEST使能(Rpd) |

0* |

-R120 |

0:使能ARM ICE JTAG连接(CoreSight) |

||

1 |

+R120 |

1:使能SCAN或BSCAN测试 |

||

JTAG_SEL |

JTAG_SEL |

— |

— |

SM JTAG端口选择(Rpd) |

0* |

-R121 |

0:ARM ICE JTAG连接 |

||

1 |

+R121 |

1:为工厂预留 |

||

POR_EN |

POR_EN |

— |

— |

上电复位(POR)旁路(Rpu) |

0 |

+R4 |

0:旁路片内POR发生器 |

||

1* |

-R4 |

1:使能片内POR发生器 |

||

PWM[0] |

cpuRstByps |

— |

— |

CPU复位旁路Strap(Rpd) |

0* |

-R116 |

0:使能CPU分区内的复位逻辑 |

||

1 |

+R116 |

1:旁路CPU分区内的复位逻辑 |

||

SPI2_SCLK |

pllPwrDown |

— |

— |

|

0* |

—R123 |

0:上电 |

||

1 |

+R123 |

1:下电 |

||

USB2_DRV _ |

pllByps |

— |

— |

PLL/MEM/CPU PLL旁路标识 |

VBUS |

||||

0* |

—R124 |

0:无旁路 |

||

1 |

+R124 |

1:所有PLL均被旁路 |

||

SPI2_SS0n |

software_strap[1] |

— |

— |

软件用的Straps(Rpd) |

0* |

—R117 |

— |

||

1 |

+R117 |

— |

||

SPI1_SDO[0] |

software_strap[2] |

— |

— |

软件用的Straps(Rpd) |

0* |

-R118 |

— |

||

1 |

+R118 |

— |

||

SPI1_SCLK[1] |

software_strap[3] |

— |

— |

软件用的Straps(Rpd) |

0* |

-R119 |

— |

||

1 |

+R119 |

— |

||

I2S1_DO |

boot_src[0] |

— |

— |

CPU boot源 位[0](Rpu)。 请参阅 boot_src[1:0]。

|

0* |

R105 |

从SPI启动ROM boot。 |

||

1 |

R107 |

从NAND启动ROM boot。 |

||

I2S2_DO |

boot_src[1] |

— |

— |

CPU boot源 位[1](Rpu)。 请参阅 boot_src[1:0]。

|

0 |

R108 |

从SPI启动ROM boot。 |

||

1* |

R106 |

从eMMC启动ROM boot。 |

||

I2S3_DO |

Legacy_boot |

— |

— |

减少复位等待时间的Strap(Rpd) |

0* |

-R122 |

0:2毫秒 |

||

1 |

+R122 |

1:20毫秒 |

Net名称 |

Strap名称 |

|

|

|

|---|---|---|---|---|

USB_BOOTn |

USB-Boot |

— |

— |

ROM代码使用此strap来确定是否从USB启动(Rpu)。 |

0 |

— |

0:在系统复位de-assertion时, 当USB—BOOT按钮被按下,从USB启动。 |

||

1* |

— |

1:从boot_src[1]选择的设备启动。 |

||

CONN-SPI- VDDIO1P8.BOOT_SRC1 |

SD-Boot |

— |

— |

ROM代码使用此Strap来确定是否从SD_Card启动(Rpu)。 |

0 |

— |

0:在系统复位de-assertion时, 当SD_Boot接头连上,从SD_Card启动。 |

||

1* |

— |

1:当SD_Boot接头断开,从boot_src[1]选择的设备启动。 |

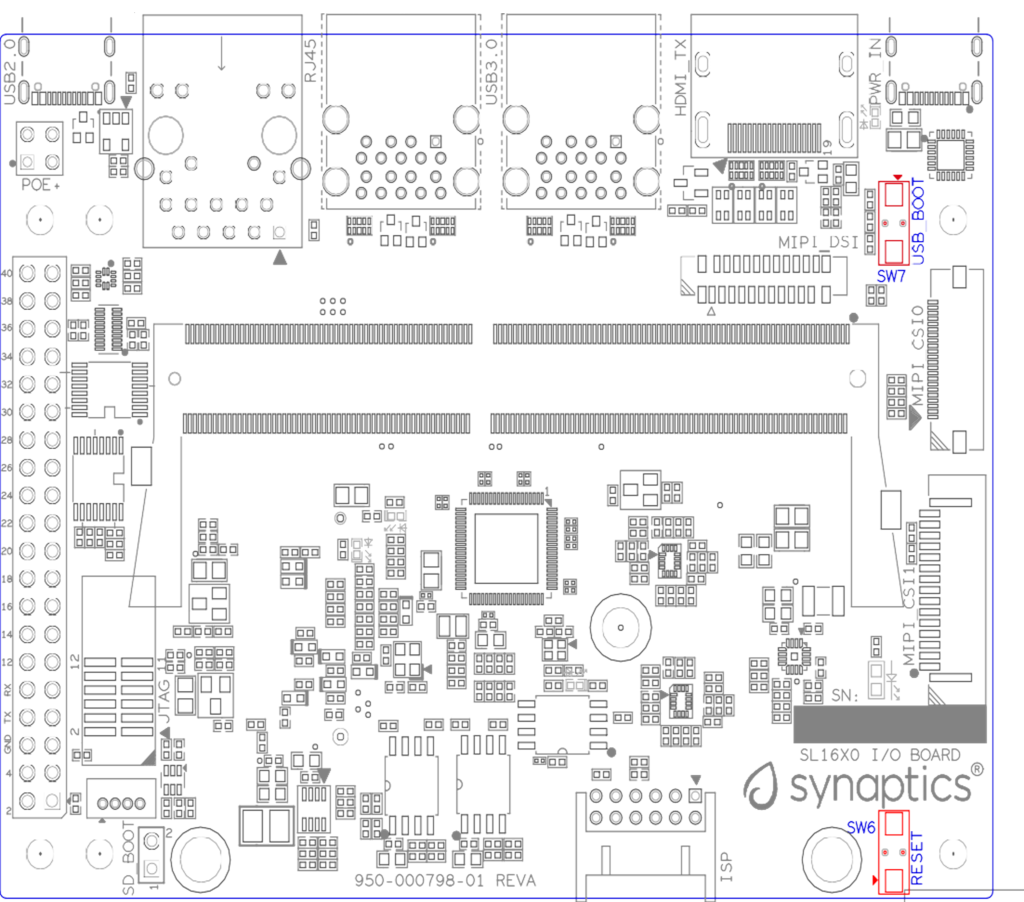

硬件手动按钮设置

Switch Block |

类型 |

设置 |

功能 |

|---|---|---|---|

SW6(RESET) |

瞬时按钮 |

按压 |

SL1620复位键置位 |

松开 |

Key de-asserted |

||

SW7(USB_BOOT) |

瞬时按钮 |

按压 |

USB启动按键被激活。 需要组合RESET按钮。 请阅读以下步骤,了解如何进入USB-boot模式。 |

松开 |

Key de-asserted |

要进入USB引导模式, 请执行以下步骤:

备注

在执行这些步骤之前, 请确保USB驱动已成功安装在PC主机端。 详情请参阅 Astra Yocto Linux用户指南 。

按下RESET按钮,向SL1620发出系统复位信号。

保持按住RESET按键,同时按下USB_BOOT按键,保持1—2秒。

在按住USB_BOOT按键的同时松开RESET按键,使SL1620进入USB启动模式。

检查并等待Console打印消息。

当Console打印返回成功进入USB boot后, 即可松开USB_boot按钮。

I/O板上手动按钮的位置图

硬件跳线设置

Ref Des |

类型 |

Pin连接 |

描述 |

|---|---|---|---|

JP1 |

2x1 2.54mm接头 |

1-2 |

SD_Boot 选择 |

|

|||

|

要进入SD-Boot模式,请执行以下步骤:

在执行这些步骤之前,请确保烧好固件的SD卡被插在核心模块的SD插槽上。

上电前请用2.54毫米跳线帽短接SD_boot接头。

系统上电,然后从SD卡启动。

I/O板上跳线的位置图 显示了I/O板上的接头位置。

I/O板上跳线的位置图

SL1620评估系统连接器

核心模块正面的连接器位置

核心模块正面位置图

核心模块背面的连接器位置

核心模块背面位置图

核心模块连接器定义

主要 Ref Des |

连接的板卡/设备 (Ref Des,如有) |

功能 |

注释 |

|---|---|---|---|

J31 |

MicroSD卡 |

SDIO卡 |

用于micro-SD类型的存储卡扩展。 |

J35 |

LCD |

LCD |

通过54针FPC电缆连接LCD面板子卡。 |

J37 |

Line out |

模拟音频L/R |

音频L/R输出到3.5mm插孔。 |

U2、U3 |

DMIC_L/R |

PDM |

数字MIC_L/R输入。 |

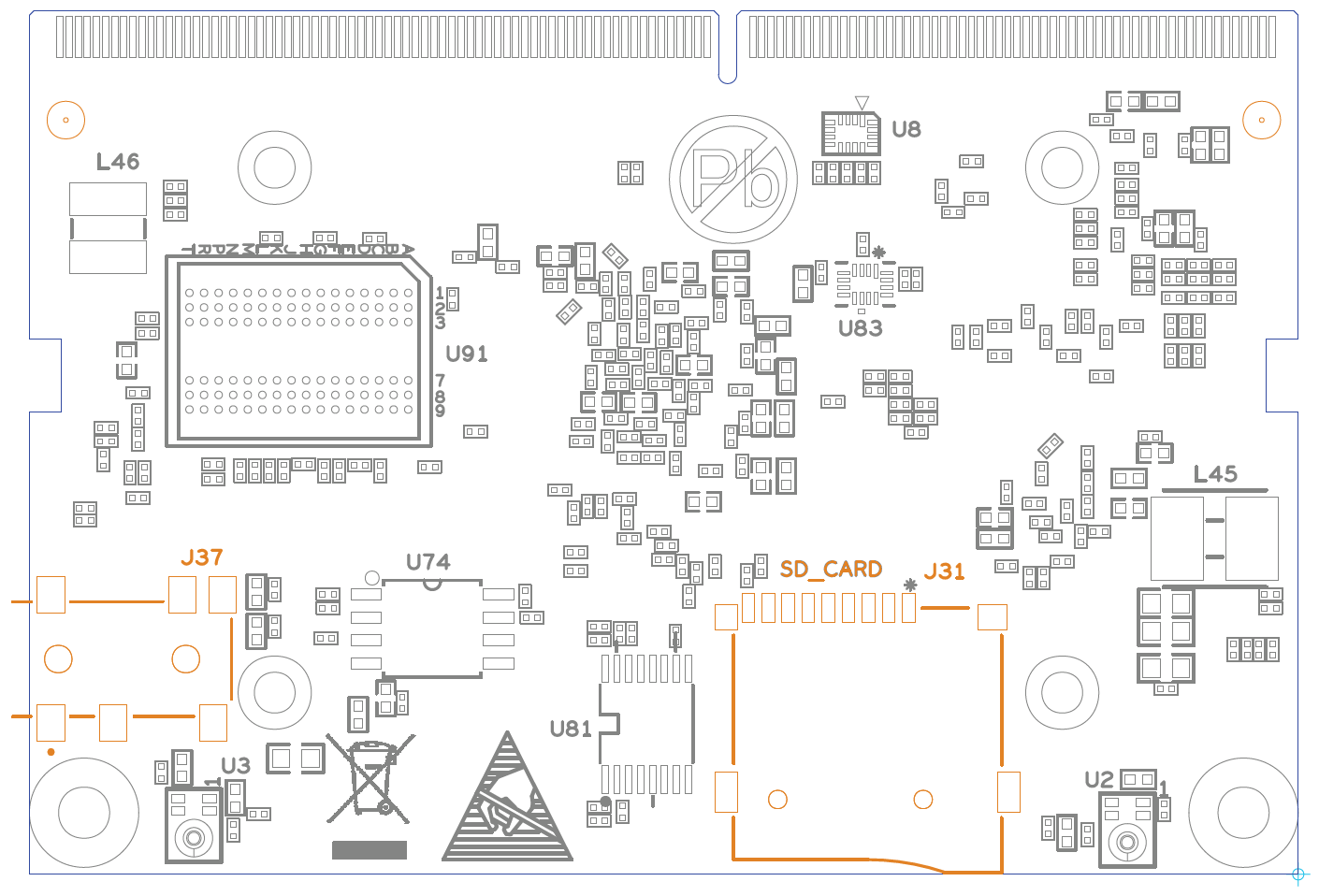

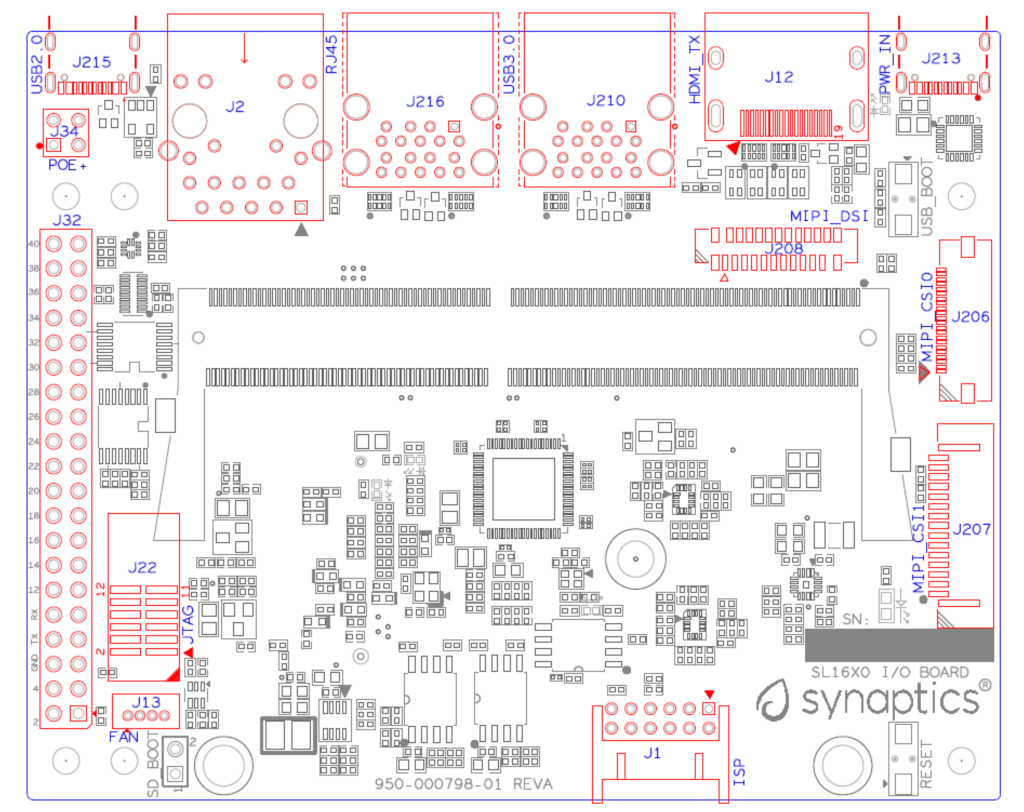

I/O板正面的连接器位置

I/O板正面的位置图

I/O板背面的连接器位置

I/O板背面的位置图

I/O板连接器定义

主要 Ref Des |

连接的板卡/设备 (Ref Des,如有) |

功能 |

注释 |

|---|---|---|---|

J1 |

ISP D/C |

SPI |

12针子卡,用于支持核心模块上离线编程的SPI NOR闪存。 |

J2 |

RJ45电缆 |

千兆以太网 |

用于有线以太网连接。 |

J12 |

HDMI Sink |

HDMI TX |

SL1620不适用。 |

J13 |

风扇 |

散热器 w/ FAN |

PWM有源风扇。 |

J17 |

M.2 2230 D/C |

SDIO和PCIe |

通过SDIO连接1x 1/2x2 WiFi/蓝牙卡。PCIe不适用于SL1620。 |

J22 |

调试板 |

JTAG |

调试用的XDB调试器 |

J32 |

40针接头 |

UART、I2C、SPI、PDM、I2SI/O 、GPIO、STS 1、PWM、ADC |

灵活支持各种D/C。 |

J34 |

PoE + D/C |

Poe + |

4针PoE+子卡,支持向40针接头附加5V电压。 |

J206 |

MIPI-CSI0 适配器 |

MIPI-CSI |

SL1620不适用。 |

J207 |

MIPI-CSI1 适配器 |

MIPI-CSI |

SL1620不适用。 |

J208 |

MIPI-DSI 适配器 |

MIPI—DSI |

用于 MIPI—DSI x4 lane 扩展,如面板。 |

J210 |

USB设备 |

USB 3.0 x2 |

仅适用于设备模式下的USB3.0扩展。 |

J213 |

TypeC电源 |

电源 |

Astra 开发套件的额定功率为 15V/1.8A。 |

J215 |

usb设备 |

USB2.0 OTG |

用于在主机或设备模式下的USB2.0扩展。 |

J216 |

USB设备 |

USB 3.0 x2 |

仅适用于设备模式下的USB3.0扩展。 |

子卡

一套为Astra 开发套件系统扩展各种I/O外围功能的子卡。 不同的制造商可以使用各自的实现不同I/O功能的子卡来提供完整设备。

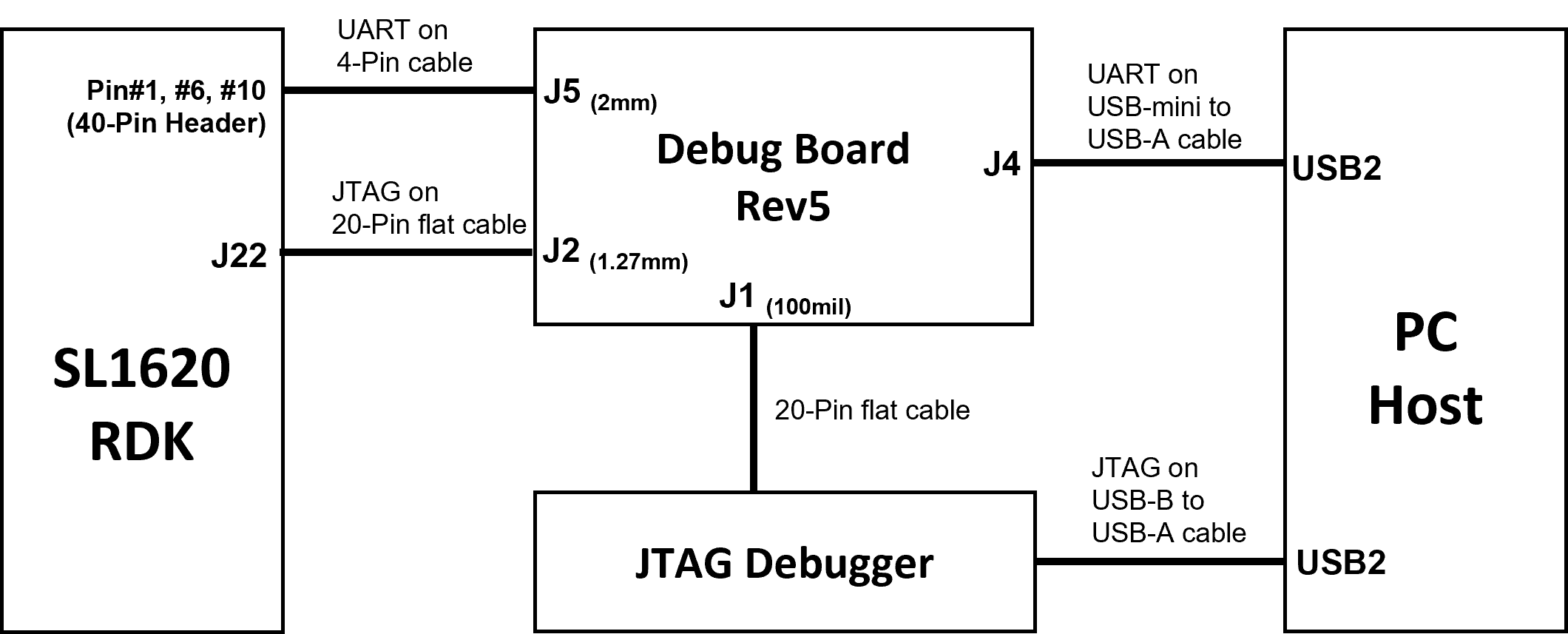

调试板

调试板(Rev5)允许用户在PC主机上通过JTAG使用调试器与SL1620系统通信。 使用20针扁平电缆连接评估系统和调试板时,请将调试板侧2x10电缆插座的引脚1与评估系统上2x6接头J22的引脚1对齐。

备注

在PC主机上,用户可以使用通用的低成本UART转USB线通过UART口与SL1620通信。 关于可用零部件清单,请参阅Astra系列 AI开发套件网页。 作为备选,调试板也提供了基于Silicon Labs CP2102的桥接功能。 所需的虚拟COM端口驱动程序,可从 供应商网站 下载并安装在主机上。

评估系统上的UART和PC主机的USB是数字隔离的, 无直接导电路径,消除了下电时的接地回路和back-drive问题。

调试板的UART及JTAG连接 显示了调试板上UART及JTAG通信的便利连接。

调试板的UART及JTAG连接

M.2卡

M.2 E—Key插座J17用于M.2 form factor的各种模块。 典型应用模块支持具有SDIO或PCIE信号接口的Wi-Fi/BT设备。

可用模块:

Ampak AP12611_M2 with SYN43711 WiFi6E/BT5.3 1x1 over SDIO on M.2 adaptor

260针SODIMM定义

260针SODIMM连接器(PN: TE_2309413-1)连接核心模块和I/O板。 260针SODIMM定义 显示了260针的分配。

分配 |

Pin# |

260针 SODIMM |

Pin# |

分配 |

|---|---|---|---|---|

GePHY_RSTn(来自IO_Exp) |

2 |

1 |

n/a |

|

SPI1_SDO && STRP[SS2] |

4 |

3 |

n/a |

|

SPI1_SCLK && STRP[SS3] |

6 |

5 |

n/a |

|

LCD_RSTn(来自IO_EXP) |

8 |

7 |

n/a |

|

n/a |

10 |

9 |

n/a |

|

SPI1_SDI |

12 |

11 |

n/a |

|

SPI1_SS0n |

14 |

13 |

n/a |

|

External_Boot_SRC0 |

16 |

15 |

n/a |

|

USB-C_Logic_INTn |

18 |

17 |

n/a |

|

SD-CARD_PPWR_EN |

20 |

19 |

n/a |

|

SD-CARD_VIO_SEL |

22 |

21 |

n/a |

|

LCD_TP_IRQ |

24 |

23 |

n/a |

|

GND |

26 |

25 |

n/a |

|

n/a |

28 |

27 |

n/a |

|

n/a |

30 |

29 |

n/a |

|

GND |

32 |

31 |

n/a |

|

n/a |

34 |

33 |

n/a |

|

n/a |

36 |

35 |

n/a |

|

GND |

38 |

37 |

n/a |

|

n/a |

40 |

39 |

n/a |

|

n/a |

42 |

41 |

n/a |

|

GND |

44 |

43 |

n/a |

|

USB2_Dn |

46 |

45 |

n/a |

|

USB2_Dp |

48 |

47 |

n/a |

|

GND |

50 |

49 |

n/a |

|

USB3_RXp |

52 |

51 |

n/a |

|

USB3_RXn |

54 |

53 |

GND |

|

GND |

56 |

55 |

n/a |

|

USB3_TXp |

58 |

57 |

n/a |

|

USB3_TXn |

60 |

59 |

GND |

|

GND |

62 |

61 |

n/a |

|

USB3_USB20.Dp |

64 |

63 |

n/a |

|

USB3_USB20.Dn |

66 |

65 |

GND |

|

GND |

68 |

67 |

n/a |

|

USB2_IDPIN |

70 |

69 |

n/a |

|

PWR_OTG_VBUS |

72 |

71 |

GND |

|

PWR_USB3_VBUS |

74 |

73 |

n/a |

|

I2S3_BCLK |

76 |

75 |

n/a |

|

I2S3_DI |

78 |

77 |

GND |

|

I2S3_DO |

80 |

79 |

n/a |

|

2S3_LRCK |

82 |

81 |

n/a |

|

I2S1_DI |

84 |

83 |

GND |

|

GPIO[22] |

86 |

85 |

n/a |

|

PDM_DI[1] |

88 |

87 |

n/a |

|

PDM_CLKIO |

90 |

89 |

GND |

|

TW1_SCL |

92 |

91 |

n/a |

|

TW1_SDA |

94 |

93 |

n/a |

|

GPIO-EXP_0_2 |

96 |

95 |

GND |

|

FAN_TACH_Control |

98 |

97 |

n/a |

|

n/a |

100 |

99 |

n/a |

|

FAN_PWM |

102 |

101 |

GND |

|

I2S1_BCLK |

104 |

103 |

n/a |

|

EXPANDER_INT—REQn |

106 |

105 |

n/a |

|

BOOT_SRC1 |

108 |

107 |

GND |

|

I2S1_DO0 |

110 |

109 |

n/a |

|

I2S1_MCLK |

112 |

111 |

n/a |

|

I2S1_LRCK |

114 |

113 |

GND |

|

PWM2 |

116 |

115 |

MIPI_DSI_TD0n |

|

GPIO[2] |

118 |

117 |

MIPI_DSI_TD0p |

|

URT0_TXD |

120 |

119 |

GND |

|

URT0_RXD |

122 |

121 |

MIPI_DSI_TD1n |

|

SPI2_SDI |

124 |

123 |

MIPI_DSI_TD1p |

|

SPI2_SCLK |

126 |

125 |

GND |

|

SPI2_SDO |

128 |

127 |

MIPI_DSI_TCKp |

|

SPI2_SS3n |

130 |

129 |

MIPI_DSI_TCKn |

|

USB2_OCn |

132 |

131 |

GND |

|

SPI2_SS1n |

134 |

133 |

MIPI_DSI_TD3n |

|

SPI2_SS0n |

136 |

135 |

MIPI_DSI_TD3p |

|

TW1_SDA |

138 |

137 |

GND |

|

TW1_SCL |

140 |

139 |

MIPI_DSI_TD2p |

|

n/a |

142 |

141 |

MIPI_DSI_TD2n |

|

n/a |

144 |

143 |

GND |

|

SPI2_SDO_3V3 |

146 |

145 |

GND |

|

SPI2_SDI_3V3 |

148 |

147 |

n/a |

|

SPI2_CLK_3V3 |

150 |

149 |

n/a |

|

n/a |

152 |

151 |

GND |

|

USB-C_Logic_INTn |

154 |

153 |

n/a |

|

n/a |

156 |

155 |

n/a |

|

n/a |

158 |

157 |

GND |

|

Levershift_EN# 用于40P接头 |

160 |

159 |

n/a |

|

n/a |

162 |

161 |

n/a |

|

RSTIn @ PU |

164 |

163 |

GND |

|

JTAG_TDO |

166 |

165 |

n/a |

|

JTAG_TDI.SoC_WakeUp# |

168 |

167 |

n/a |

|

JTAG_TMS |

170 |

169 |

GND |

|

n/a |

172 |

171 |

n/a |

|

n/a |

174 |

173 |

n/a |

|

GPIO[48] |

176 |

175 |

GND |

|

TW2_SDA |

178 |

177 |

n/a |

|

TW2_SCL |

180 |

179 |

JTAG_TCK |

|

TW0_SDA |

182 |

181 |

GPIO[47] |

|

TW0_SCL |

184 |

183 |

JTAG_TRSTn |

|

URT1A_CTSn,用于M.2 |

186 |

185 |

GPIO—EXP_0_7 |

|

URT1A_RTSn,用于M.2 |

188 |

187 |

URT1A_RXD,用于M.2 |

|

PWM1 |

190 |

189 |

GPIO[55] |

|

GND |

192 |

191 |

URT1A_TXD,用于M.2 |

|

PWR_1V8 |

194 |

193 |

n/a |

|

PWR_1V8 |

196 |

195 |

n/a |

|

PWR_1V8_CTL |

198 |

197 |

n/a |

|

PWR_1V8_CTL |

200 |

199 |

n/a |

|

PWR_3V3_CTL |

202 |

201 |

n/a |

|

PWR_3V3_CTL |

204 |

203 |

n/a |

|

GND |

206 |

205 |

USB_BOOTn |

|

M.2_WIFI_SDIO_CLK |

208 |

207 |

SDIO_MUX_SEL(来自IO_EXP) |

|

GND |

210 |

209 |

ETHERNET_LINK_LED |

|

M.2_WIFI_SDIO_CMD |

212 |

211 |

ETHERNET_DUPLX_LED |

|

GND |

214 |

213 |

GND |

|

M.2_WIFI_SDIO_D0 |

216 |

215 |

RJ45_MDIP0 |

|

GND |

218 |

217 |

RJ45_MDIN0 |

|

M.2_WIFI_SDIO_D1 |

220 |

219 |

GND |

|

GND |

222 |

221 |

RJ45_MDIP1 |

|

M.2_WIFI_SDIO_D2 |

224 |

223 |

RJ45_MDIN1 |

|

GND |

226 |

225 |

GND |

|

M.2_WIFI_SDIO_D3 |

228 |

227 |

RJ45_MDIP2 |

|

GND |

230 |

229 |

RJ45_MDIN2 |

|

PWR_3V3 |

232 |

231 |

GND |

|

PWR_3V3 |

234 |

233 |

RJ45_MDIP3 |

|

PWR_3V3 |

236 |

235 |

RJ45_MDIN3 |

|

PWR_3V3 |

238 |

237 |

GND |

|

PWR_3V3 |

240 |

239 |

PWR_BL,用于LCD背光 |

|

PWR_3V3 |

242 |

241 |

PWR_BL,用于LCD背光 |

|

GND |

244 |

243 |

GND |

|

GND |

246 |

245 |

GND |

|

GND |

248 |

247 |

GND |

|

GND |

250 |

249 |

GND |

|

PWR_5V |

252 |

251 |

PWR_5V |

|

PWR_5V |

254 |

253 |

PWR_5V |

|

PWR_5V |

256 |

255 |

PWR_5V |

|

PWR_5V |

258 |

257 |

PWR_5V |

|

PWR_5V |

260 |

259 |

PWR_5V |

40针接头

40针GPIO接头, 引脚间距为0.1英寸(2.54mm),位于I/O板正面的边缘。 任何通用3.3V引脚的各种可选功能都可通过软件配置。详情请参阅 SL1620 Datasheet 。

40针接头定义

标准接口配置的引脚解复用

本节介绍SL1620评估系统的引脚解复用配置。 关于片上系统(SoC),请参阅 SoC引脚解复用用法 。

SL1620片上系统 (SoC) Domain |

||||

|---|---|---|---|---|

Pad/Pin 名称 |

缺省用法 |

方向 |

模式设置 |

|

SDIO |

SDIO_CDn |

I:SDIOA_CDn |

IN |

MODE_1 |

SDIO_WP |

IO:GPIO[55] |

IN/OUT |

MODE_0 |

|

SPI1 |

SPI1_SS0n |

O:SPI1_SS0n |

OUT |

MODE_0 |

SPI1_SS1n |

IO:GPIO[4] |

IN |

MODE_2 |

|

SPI1_SS2n |

I:URT0A_RXD |

IN |

MODE_0 |

|

SPI1_SS3n |

O:URT0A_TXD |

OUT |

MODE_0 |

|

SPI1_SDO |

O:SPI1_SDO |

OUT |

MODE_0 |

|

SPI1_SDI |

I:SPI1_SDI |

IN |

MODE_0 |

|

SPI1_SCLK |

O:SPI1_SCLK |

OUT |

MODE_0 |

|

SPI2 |

SPI2_SS0n |

O:SPI2_SS0n |

OUT |

MODE_1 |

SPI2_SS1n |

O:SPI2_SS1n |

OUT |

MODE_1 |

|

SPI2_SS2n |

O:SPI2_SS2n |

OUT |

MODE_2 |

|

SPI2_SS3n |

O:SPI2_SS3n |

OUT |

MODE_2 |

|

SPI2_SDO |

O:SPI2_SDO |

OUT |

MODE_1 |

|

SPI2_SDI |

I:SPI2_SDI |

IN |

MODE_1 |

|

SPI2_SCLK |

O:SPI2_SCLK |

OUT |

MODE_1 |

|

UART |

URT1_RXD |

I:URT1A_RXD |

IN |

MODE_2 |

URT1_TXD |

O:URT1A_TXD |

OUT |

MODE_2 |

|

TWSI |

TW0_SCL |

IO:TW0A_SCL |

OUT |

MODE_0 |

TW0_SDA |

IO:TW0A_SDA |

IN/OUT |

MODE_0 |

|

TW1_SCL |

IO:TW1_SCL |

OUT |

MODE_0 |

|

TW1_SDA |

IO:TW1_SDA |

IN/OUT |

MODE_0 |

|

TW2_SCL |

IO:TW2_SCL |

OUT |

MODE_1 |

|

TW2_SDA |

IO:TW2_SDA |

IN/OUT |

MODE_1 |

|

TW3_SCL |

O:URT1A_RTSn |

OUT |

MODE_2 |

|

TW3_SDA |

I:URT1A_CTSn |

IN |

MODE_2 |

|

USB2 |

USB2_DRV_VBUS |

O:GPIO[51] |

OUT |

MODE_1 |

PWM |

PWM[0] |

O:PWM[0] |

OUT |

MODE_1 |

PWM[1] |

O:PWM[1] |

OUT |

MODE_1 |

|

PWM[2] |

O:PWM[2] |

OUT |

MODE_1 |

|

PWM[3] |

O:PWM[3] |

OUT |

MODE_1 |

|

RGMII |

RGMII_TXC |

O:RGMII_TXC |

OUT |

MODE_1 |

RGMII_TXD[0] |

O:RGMII_TXD[0] |

OUT |

MODE_1 |

|

RGMII_TXD[1] |

O:RGMII_TXD[1] |

OUT |

MODE_1 |

|

RGMII_TXD[2] |

O:RGMII_TXD[2] |

OUT |

MODE_1 |

|

RGMII_TXD[3] |

O:RGMII_TXD[3] |

OUT |

MODE_1 |

|

RGMII_TXCTL |

O:RGMII_TXCTL |

OUT |

MODE_1 |

|

RGMII_RXC |

I:RGMII_RXC |

IN |

MODE_1 |

|

RGMII_RXD[0] |

I:RGMII_RXD[0] |

IN |

MODE_1 |

|

RGMII_RXD[1] |

I:RGMII_RXD[1] |

IN |

MODE_1 |

|

RGMII_RXD[2] |

I:RGMII_RXD[2] |

IN |

MODE_1 |

|

RGMII_RXD[3] |

I:RGMII_RXD[3] |

IN |

MODE_1 |

|

RGMII_RXCTL |

I:RGMII_RXCTL |

IN |

MODE_1 |

|

I2S1 |

I2S1_DO |

O:I2S1_DO |

OUT |

MODE_1 |

I2S1_DI |

I:I2S1_DI |

IN |

MODE_1 |

|

I2S1_LRCK |

IO:I2S1_LRCK |

IN/OUT |

MODE_1 |

|

I2S1_BCLK |

IO:I2S1_BCLK |

IN/OUT |

MODE_1 |

|

I2S1_MCLK |

IO:I2S1_MCLK |

OUT |

MODE_1 |

|

I2S2 |

I2S2_DO |

O:I2S2_DO |

OUT |

MODE_1 |

I2S2_DI |

IO:GPIO[22] |

IN/OUT |

MODE_0 |

|

I2S2_LRCK |

IO:I2S2_LRCK |

IN/OUT |

MODE_1 |

|

I2S2_BCLK |

IO:I2S2_BCLK |

IN/OUT |

MODE_1 |

|

I2S3 |

I2S3_DO |

O:I2S3_DO |

OUT |

MODE_1 |

I2S3_DI |

I:I2S3_DI |

IN |

MODE_1 |

|

I2S3_LRCK |

IO:I2S3_LRCK |

IN/OUT |

MODE_1 |

|

I2S3_BCLK |

IO:I2S3_BCLK |

IN/OUT |

MODE_1 |

|

PDM |

PDM_CLKIO |

IO:PDM_CLKIO |

OUT |

MODE_1 |

PDM_DI[0] |

I:PDM_DI[0] |

IN |

MODE_1 |

|

PDM_DI[1] |

I:PDM_DI[1] |

IN |

MODE_1 |

|

JTAG |

TMS |

IO:GPIO[0] |

IN |

MODE_1 |

TDI |

IO:GPIO[1] |

IN |

MODE_1 |

|

TDO |

IO:GPIO[2] |

IN/OUT |

MODE_1 |

|

GPIO_A |

GPIO_A[0] |

IO:RGMIIA_MDIO |

IN/OUT |

MODE_1 |

GPIO_A[1] |

O:RGMIIA_MDC |

OUT |

MODE_1 |

|

GPIO_A[2] |

IO:GPIO[48] |

IN/OUT |

MODE_0 |

|

GPIO_A[3] |

IO:GPIO[47] |

IN/OUT |

MODE_0 |

|

NAND |

NFALE |

O:NFALE |

OUT |

MODE_1 |

NFLCS |

O:NFLCS |

OUT |

MODE_1 |

|

LCDC |

LCDD0 |

IO:LCDD0 |

IN/OUT |

MODE_1 |

LCDD1 |

IO:LCDD1 |

IN/OUT |

MODE_1 |

|

LCDD2 |

IO:LCDD2 |

IN/OUT |

MODE_1 |

|

LCDD3 |

IO:LCDD3 |

IN/OUT |

MODE_1 |

|

LCDD4 |

IO:LCDD4 |

IN/OUT |

MODE_1 |

|

LCDD5 |

IO:LCDD5 |

IN/OUT |

MODE_1 |

|

LCDD6 |

IO:LCDD6 |

IN/OUT |

MODE_1 |

|

LCDD7 |

IO:LCDD7 |

IN/OUT |

MODE_1 |

|

LCDD8 |

IO:LCDD8 |

IN/OUT |

MODE_1 |

|

LCDD9 |

IO:LCDD9 |

IN/OUT |

MODE_1 |

|

LCDD10 |

IO:LCDD10 |

IN/OUT |

MODE_1 |

|

LCDD11 |

IO:LCDD11 |

IN/OUT |

MODE_1 |

|

LCDD12 |

IO:LCDD12 |

IN/OUT |

MODE_1 |

|

LCDD13 |

IO:LCDD13 |

IN/OUT |

MODE_1 |

|

LCDD14 |

IO:LCDD14 |

IN/OUT |

MODE_1 |

|

LCDD15 |

IO:LCDD15 |

IN/OUT |

MODE_1 |

|

LCDD16 |

IO:LCDD16 |

IN/OUT |

MODE_1 |

|

LCDD17 |

IO:LCDD17 |

IN/OUT |

MODE_1 |

|

LCDD18 |

IO:LCDD18 |

IN/OUT |

MODE_1 |

|

LCDD19 |

IO:LCDD19 |

IN/OUT |

MODE_1 |

|

LCDD20 |

IO:LCDD20 |

IN/OUT |

MODE_1 |

|

LCDD21 |

IO:LCDD21 |

IN/OUT |

MODE_1 |

|

LCDD22 |

IO:LCDD22 |

IN/OUT |

MODE_1 |

|

LCDD23 |

IO:LCDD23 |

IN/OUT |

MODE_1 |

|

LPCLK |

O:LPCLK |

OUT |

MODE_1 |

|

LCDGPIO0 |

O:LCDGPIO0 |

OUT |

MODE_1 |

|

LCDGPIO1 |

O:LCDGPIO1 |

OUT |

MODE_1 |

|

LCDGPIO2 |

O:LCDGPIO2 |

OUT |

MODE_1 |

|

LCDGPIO3 |

O:LCDGPIO3 |

OUT |

MODE_1 |

GPIO/GPO配置的引脚解复用

本节介绍SoC域的引脚解复用GPIO/GPO用法。

SL1620 SoC |

可用性 |

方向 |

默认功能 |

GPIO 信号 |

|---|---|---|---|---|

GPIO/GPO |

||||

GPIO[0] |

MODE_1 |

IN |

GPIO_EXP_INTn(CM) |

0:GPIO扩展器触发中断(核心模块) |

1:无中断 |

||||

GPIO_X[0] |

不可用 |

IN/OUT |

IO:LCDD8 |

— |

GPIO[1] |

MODE_1 |

IN |

WiFi_WAKE_UP# |

0:由WiFi触发的唤醒 |

1:无唤醒触发 |

||||

GPIO_X[1] |

不可用 |

IN/OUT |

IO:LCDD9 |

— |

GPIO[2] |

MODE_1 |

IN/OUT |

IO:LCDD16 |

至40针接头 |

GPIO_X[2] |

不可用 |

IN/OUT |

O:SM_FE_LED[0] |

— |

GPIO[3] |

不可用 |

OUT |

O:SPI1_SS0n |

— |

GPIO[4] |

MODE_2 |

IN |

GPIO_EXP_INTn(I/O板) |

0:GPIO扩展器触发中断(I/O板) |

1:无中断 |

||||

GPIO[5] |

MODE_0 |

IN |

I:URT0A_RXD |

至40针接头 |

GPIO[6] |

MODE_0 |

OUT |

O:URT0A_TXD |

至40针接头 |

GPO[7] |

不可用 |

OUT |

O:SPI1_SDO |

— |

GPO[8] |

不可用 |

OUT |

O:SPI1_SCLK |

— |

GPIO[9] |

不可用 |

IN |

I:SPI1_SDI |

— |

GPIO[10] |

MODE_0 |

OUT |

IO:TW0A_SCL |

至 40针接头 / Display IF/ GPIO_EXP_CM |

GPIO_X[10] |

不可用 |

IN/OUT |

O:LCDGPIO3 |

— |

GPIO[11] |

MODE 0 |

IN/OUT |

IO:TW0A_SDA |

至 40针接头 / Display IF/ GPIO_EXP_CM |

GPIO_X[11] |

MODE 0 |

IN |

GePHY_INTB |

0:由GePHY触发的中断 |

1:无中断 |

||||

GPIO[12] |

MODE_0 |

OUT |

IO:TW1_SCL |

至 40针接头/ M.2/ GPIO_EXP_IO |

GPIO_X[12] |

不可用 |

IN/OUT |

IO:LCDD0 |

— |

GPIO[13] |

MODE_0 |

IN/OUT |

IO:TW1_SDA |

至 40针接头/ M.2/ GPIO_EXP_IO |

GPIO_X[13] |

不可用 |

IN/OUT |

IO:LCDD1 |

— |

GPIO[14] |

MODE_1 |

OUT |

IO:I2S1_LRCK |

至40针接头 |

GPIO_X[14] |

不可用 |

IN/OUT |

IO:LCDD23 |

— |

GPIO[15] |

MODE_1 |

OUT |

IO:I2S1_BCLK |

至40针接头 |

GPIO_X[15] |

不可用 |

OUT |

O:LPCLK |

— |

GPO[16] |

MODE_1 |

OUT |

O:I2S1_DO |

至40针接头 |

GPIO_X[16] |

不可用 |

OUT |

O:LCDGPIO0 |

— |

GPIO[17] |

MODE_1 |

OUT |

IO:I2S1_MCLK |

至40针接头 |

GPIO_X[17] |

不可用 |

OUT |

O:LCDGPIO1 |

— |

GPIO[18] |

MODE_1 |

IN |

I:I2S1_DI |

至40针接头 |

GPIO_X[18] |

不可用 |

OUT |

O:LCDGPIO2 |

— |

GPIO[19] |

不可用 |

OUT |

IO:I2S2_LRCK |

— |

GPIO_X[19] |

不可用 |

OUT |

O:RGMII_TXD[0] |

— |

GPIO[20] |

不可用 |

OUT |

IO:I2S2_BCLK |

— |

GPIO_X[20] |

不可用 |

OUT |

O:RGMII_TXD[1] |

— |

GPO[21] |

不可用 |

OUT |

O:I2S2_DO |

— |

GPIO_X[21] |

不可用 |

OUT |

O:RGMII_TXD[2] |

— |

GPIO[22] |

MODE_0 |

IN/OUT |

IO:GPIO[22] |

至40针接头 |

GPIO_X[22] |

不可用 |

OUT |

O:RGMII_TXD[3] |

— |

GPIO[23] |

MODE_1 |

IN |

I:PDM_DI[1] |

至40针接头 |

GPIO[24] |

不可用 |

IN |

I:PDM_DI[0] |

— |

GPIO[25] |

MODE_1 |

OUT |

IO:PDM_CLKIO |

至板载 40针接头 / DMIC |

GPIO[26] |

不可用 |

OUT |

IO:I2S3_LRCK |

— |

GPIO[27] |

不可用 |

OUT |

IO:I2S3_BCLK |

— |

GPO[28] |

不可用 |

OUT |

O:I2S3_DO |

— |

GPIO[29] |

不可用 |

IN |

I:I2S3_DI |

— |

GPO[30] |

MODE_1 |

OUT |

O:SPI2_SS0n |

至40针接头 |

GPIO[31] |

MODE_1 |

OUT |

O:SPI2_SS1n |

至40针接头 |

GPIO_X[31] |

不可用 |

IN |

I:RGMII_RXD[0] |

— |

GPIO[32] |

不可用 |

OUT |

O:SPI2_SS2n |

— |

GPIO_X[32] |

不可用 |

IN |

I:RGMII_RXD[1] |

— |

GPIO[33] |

MODE_2 |

OUT |

O:SPI2_SS3n |

至40针接头 |

GPIO_X[33] |

不可用 |

IN |

I:RGMII_RXD[2] |

— |

GPO[34] |

MODE_1 |

OUT |

O:SPI2_SDO |

至 40-Pin Header / LCDC |

GPO[35] |

MODE_1 |

OUT |

O:SPI2_SCLK |

至 40-Pin Header / LCDC |

GPIO[36] |

MODE_1 |

IN |

I:SPI2_SDI |

至 40-Pin Header / LCDC |

GPIO[37] |

不可用 |

OUT |

IO:TW2_SCL |

— |

GPIO[38] |

不可用 |

IN/OUT |

IO:TW2_SDA |

— |

GPIO[39] |

不可用 |

IN |

I:URT1A_RXD |

— |

GPIO_X[39] |

不可用 |

IN/OUT |

IO:LCDD17 |

— |

GPIO[40] |

不可用 |

OUT |

O:URT1A_TXD |

— |

GPIO_X[40] |

不可用 |

IN/OUT |

IO:LCDD22 |

— |

GPIO[41] |

不可用 |

OUT |

O:URT1A_RTSn |

— |

GPIO_X[41] |

不可用 |

IN |

I:RGMII_RXD[3] |

— |

GPIO[42] |

不可用 |

IN |

I:URT1A_CTSn |

— |

GPIO_X[42] |

不可用 |

IN |

I:RGMII_RXC |

— |

GPIO[43] |

不可用 |

OUT |

O:PWM[3] |

— |

GPIO_X[43] |

不可用 |

OUT |

O:RGMII_TXC |

— |

GPIO[44] |

MODE_1 |

OUT |

O:PWM[2] |

至40针接头 |

GPIO[45] |

MODE_1 |

OUT |

O:PWM[1] |

至40针接头 |

GPO[46] |

不可用 |

OUT |

O:PWM[0] |

— |

GPIO[47] |

MODE_0 |

IN/OUT |

IO:GPIO[47] |

至40针接头 |

GPIO[48] |

MODE_0 |

IN/OUT |

IO:GPIO[48] |

至40针接头 |

GPIO[49] |

不可用 |

OUT |

O:RGMIIA_MDC |

— |

GPIO[50] |

不可用 |

IN/OUT |

IO:RGMIIA_MDIO |

— |

GPIO[51] |

MODE_1 |

OUT |

Audio_Mute |

0:静音 |

1:取消静音 |

||||

GPIO_X[51] |

不可用 |

OUT |

O:RGMII_TXCTL |

— |

GPIO[52] |

不可用 |

OUT |

O:NFALE |

— |

GPIO_X[52] |

不可用 |

IN |

I:RGMII_RXCTL |

— |

GPIO[53] |

不可用 |

OUT |

O:NFLCS |

— |

GPIO_X[53] |

不可用 |

IN |

O:RGMII_CLK_OUT |

— |

GPO[54] |

不可用 |

IN |

I:SDIOA_CDn |

— |

GPIO[55] |

MODE_0 |

IN/OUT |

IO:GPIO[55] |

至40针接头 |

GPIO[56] |

不可用 |

IN/OUT |

IO:LCDD2 |

— |

GPIO[57] |

不可用 |

IN/OUT |

IO:LCDD3 |

— |

GPIO[58] |

不可用 |

IN/OUT |

IO:LCDD4 |

— |

GPIO[59] |

不可用 |

IN/OUT |

IO:LCDD5 |

— |

GPIO[60] |

不可用 |

IN/OUT |

IO:LCDD6 |

— |

GPIO[61] |

不可用 |

IN/OUT |

IO:LCDD7 |

— |

GPIO[62] |

不可用 |

IN/OUT |

IO:LCDD10 |

— |

GPIO[63] |

不可用 |

IN/OUT |

IO:LCDD11 |

— |

GPIO[64] |

不可用 |

IN/OUT |

IO:LCDD12 |

— |

GPIO[65] |

不可用 |

IN/OUT |

IO:LCDD13 |

— |

GPIO[66] |

不可用 |

IN/OUT |

IO:LCDD14 |

— |

GPIO[67] |

不可用 |

IN/OUT |

IO:LCDD15 |

— |

GPIO[68] |

不可用 |

IN/OUT |

IO:LCDD18 |

— |

GPIO[69] |

不可用 |

IN/OUT |

IO:LCDD19 |

— |

GPIO[70] |

不可用 |

IN/OUT |

IO:LCDD20 |

— |

GPIO[71] |

不可用 |

IN/OUT |

IO:LCDD21 |

— |

通过I2C的GPIO扩展器

L1620评估系统涵盖了相当多的功能,大多数具备GPIO/GPO复用功能选项的SL1620数字引脚都可用于其他功能。 因此,GPIO扩展器被广泛应用于扩充系统控制。

扩展器 |

I2C# |

Domain |

电压 |

方向 |

功能 |

GPIO 信号 |

|---|---|---|---|---|---|---|

GPIO/GPO |

||||||

GPIO0_0 |

TW1(0x43) |

SoC |

3.3V |

OUT |

SDIO—MUX_SEL |

0:将SDIO切换到M.2 WiFi |

1:将SDIO切换到SD卡插槽 |

||||||

GPIO0_1 |

TW1(0x43) |

SoC |

3.3V |

OUT |

PWR_ON_DSI |

0:DSI面板下电 |

1:DSI面板上电 |

||||||

GPIO0_2 |

TW1(0x43) |

SoC |

3.3V |

OUT |

LCD_RST# |

0:复位LCD |

1:De-assert Reset |

||||||

GPIO0_3 |

TW1(0x43) |

SoC |

3.3V |

OUT |

GePHY_RST# |

0:复位 |

1:De-assert Reset |

||||||

GPIO0_4 |

TW1(0x43) |

SoC |

3.3V |

OUT |

STAND-BY_EN |

0:正常播放 |

1:进入待机状态且外设下电 |

||||||

GPIO0_5 |

TW1(0x43) |

SoC |

3.3V |

IN |

USB2.0_PWR_EN |

0:下电 |

1:上电 |

||||||

GPIO0_6 |

TW1(0x43) |

SoC |

3.3V |

IN |

未使用 |

— |

— |

||||||

GPIO0_7 |

TW1(0x43) |

SoC |

3.3V |

IN/OUT |

GPIO_DSI |

保留 |

保留 |

||||||

GPIO1_0 |

TW1(0x44) |

SoC |

3.3V |

IN |

USB-C_Logic_INT# |

0:状态已更改 |

1:状态未更改 |

||||||

GPIO1_1 |

TW1(0x44) |

SoC |

3.3V |

OUT |

未使用 |

— |

— |

||||||

GPIO1_2 |

TW1(0x44) |

SoC |

3.3V |

OUT |

M2—W_DISABLE1# |

0:通过 DISABLE1# 禁用 M.2 模块 |

1:De-assertion |

||||||

GPIO1_3 |

TW1(0x44) |

SoC |

3.3V |

OUT |

M2-W_HOST-WAKE# |

0:从主机向 M.2模块 发出唤醒事件 |

1:De-assertion |

||||||

GPIO1_4 |

TW1(0x44) |

SoC |

3.3V |

OUT |

SD—CARD_PWR_EN |

0:SD卡插槽下电 |

1:SD卡插槽上电 |

||||||

GPIO1_5 |

TW1(0x44) |

SoC |

3.3V |

OUT |

M2-W_DISABLE2# |

0:通过 DISABLE2# 禁用 M.2 模块 |

1:De-assertion |

||||||

GPIO1_6 |

TW1(0x44) |

SoC |

3.3V |

OUT |

SD-CARD_VIO_SEL |

0:1.8V |

1:3.3V |

||||||

GPIO1_7 |

TW1(0x44) |

SoC |

3.3V |

OUT |

LCD_TP_IRQ# |

0:中断被触发 |

1:无中断 |

||||||

GPIO0_0 |

TW0(0x43) |

SoC |

1.8V |

IN |

FAN_TECH_CON |

0:风扇出错 |

1:无中断 |

||||||

GPIO0_1 |

TW0(0x43) |

SoC |

1.8V |

IN |

AUD_JACK_DET |

0:音频插孔在位 |

1:音频插孔不在位 |

||||||

GPIO0_2 |

TW0(0x43) |

SoC |

1.8V |

IN/OUT |

GPIO_0_2 (40针接头) |

0:取决于用户定义 |

1:取决于用户定义 |

||||||

GPIO0_3 |

TW0(0x43) |

SoC |

1.8V |

OUT |

NAND_WP# |

0:写保护 |

1:可写 |

||||||

GPIO0_4 |

TW0(0x43) |

SoC |

1.8V |

OUT |

DMIC_MUTE# |

0:DMIC 静音 |

1:DMIC 解除静音 |

||||||

GPIO0_5 |

TW0(0x43) |

SoC |

1.8V |

OUT |

LevelTranslator_EN# |

0:使能电平转换器 |

1:禁用电平转换器 |

||||||

GPIO0_6 |

TW0(0x43) |

SoC |

1.8V |

IN |

USB2_USB_OC# |

0:检测到 USB2 过流 |

1:正常状态 |

||||||

GPIO0_7 |

TW0(0x43) |

SoC |

1.8V |

IN/OUT |

GPIO_0_7(40针接头) |

0:取决于用户定义 |

1:取决于用户定义 |

I2C总线

本节介绍Astra系列 AI开发套件主板 I2C 总线的用法,等价于SL1620的Two Wire Serial Interface(TWSI)总线。

I2C/TWSI 总线 |

设备 |

器件编号 |

Ref Des |

目标地址 (7位) |

位置 |

|---|---|---|---|---|---|

TW0 |

外部设备连接到MIPI_DSI连接器 |

不适用 |

J208 |

0xxx |

SL16x0 I/O 板 |

外部设备连接到40针接头 |

不适用 |

J32 |

0xXX |

SL16x0 I/O 板 |

|

外部设备连接到LCD连接器 |

不适用 |

J35 |

0xXX |

SL1620 Core Module核心模块 |

|

IC GPIO Expander |

FXL6408UMX |

U8 |

0x43 |

SL1620 Core Module核心模块 |

|

TW1 |

IC GPIO Expander |

FXL6408UMX |

u12 |

0x43 |

SL16x0 I/O 板 |

IC GPIO Expander |

FXL6408UMX |

U13 |

0x44 |

SL16x0 I/O 板 |

|

外部设备连接到40针接头 |

不适用 |

J32 |

0xXX |

SL16x0 I/O 板 |

|

TW2 |

IC REG,缺省0.8V Vout /5mV步进, 6A额定值,输入 5.5V @ Max, 带I2C的降压转换器 |

TPS628660AYCG |

u39 |

0x49 |

SL1620核心模块 |

点亮SL1620 Astra系列 AI开发套件系统

连接外部组件并执行硬件测试

执行以下步骤, 将外部组件连接到SL1620评估系统:

将TypeC电源连接到J213(PWR_IN)。

通过FPC电缆将MIPI_DSI子板与面板连接到J208。

使用以太网线将网络连接到J2(RJ45)。

将USB3.0闪存盘插入J216/J210(USB3.0)。

通过TypeC/TypeA转换器将USB2.0闪存盘插入J215(USB2.0)。

如果没有短路问题,则接通系统电源并检查电压, 如 使用任何接地测试点进行短路和电压检查 所示, LED状态如 I/O板上的LED定义 所示。

短路和电压检查点

Ref Des |

Form |

信号 |

电压 |

|---|---|---|---|

C123 |

Pad 2 |

PWR_LCD_BL |

15V +/- 2% [14.7,15.3] |

C414 |

Pad 1 |

PWR_5V |

5.2V +/- 2% [5.096,5.304] |

C6 |

Pad 1 |

PWR_3V3 |

3.3V +/- 1% [3.267,3.333] |

Q3 |

Pad 2 |

PWR_1V8 |

1.8V +/- 2% [1.764,1.836] |

C452 |

Pad 1 |

PWR_VDDM_1V2 |

1.2V +/- 2% [1.176,1.224] |

C441 |

Pad 1 |

PWR_VDDM_2V5 |

2.5V +/- 2% [2.45,2.55] |

R554 |

Pad 2 |

PWR_VCORE_FB |

Vcore_FB +/—2% |

参考资料

以下文件适用于SL1620评估系统:

SL1620 Datasheet(PN:505-001428-01)